Verific Integrates INVIO with Flagship Parser Platform

May 30, 2018

News

Integration Enables Users to Simplify, Streamline Design Environment

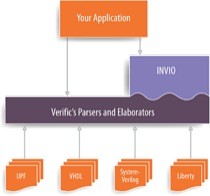

| INVIO is integrated with the Verific parser platforms. |

Verific Design Automation, the recognized leader of SystemVerilog, VHDL and UPF Parser Platforms in production and development use throughout the semiconductor industry, today announced full integration of INVIO with its flagship parser platforms.

This follows an earlier announcement that it acquired from Invionics Software the INVIO platform, with its high-level level application programming interfaces (APIs) that enable Verific users to simplify and streamline their design environment, accelerating tool development.

INVIO is SystemVerilog- and VHDL-language agnostic and offers a high level of abstraction that semiconductor company CAD support departments need for their SystemVerilog and VHDL flows. The integration included the addition of C++ APIs to INVIO, and porting of Verific’s native Liberty and UPF parsers to INVIO. The combined product line, named “Verific with INVIO,” was rolled out earlier this year and is in production use at five semiconductor companies to date, including IBM.

“Our users are pleased with the additional capabilities provided by INVIO to develop their next EDA product or custom tool development,” notes Rob Dekker, Verific’s founder and chief technology officer. “We credit a capable R&D and applications engineering group who joined Verific as part of the acquisition and did excellent work integrating INVIO with Verific and supporting the customers.”

“As early adopters of Verific with INVIO I am happy to report that we were able to deliver two internally used EDA tools on time under an aggressive schedule,” affirms Wolfgang Roesner, IBM fellow, functional verification.

Verific continues to sell its SystemVerilog, UPF and VHDL parsers as standalone solutions. INVIO is marketed and sold as an add-on. Verific’s parsers are in production and development flows throughout semiconductor companies worldwide, from emerging companies to established Fortune 500 vendors. Applications range from analysis, simulation, formal verification and synthesis to emulation and virtual prototyping, in-circuit debug and design for test. Verific distributes its Parser Platforms as C++ source code and compile on all 32 and 64 bit Unix, Linux, Mac and Windows operating systems.

Pricing is available upon request.

Verific will demonstrate its SystemVerilog, VHDL and UPF Parser Platforms, and Verific with INVIO at the Design Automation Conference (DAC) in Booth #2311 from 10 a.m. until 6 p.m. June 25-27. DAC will be held at the Moscone Center in San Francisco.

About Verific Design Automation

Verific Design Automation, with offices in Alameda, Calif., and Kolkata, India, provides SystemVerilog, Verilog, VHDL and UPF Parser Platforms that enable project groups to develop advanced electronic design automation (EDA) products quickly and cost effectively. Since 1999, Verific has shipped more than 60,000 copies of its software used worldwide by the EDA and semiconductor industry. Corporate headquarters is located at: 1516 Oak Street, Suite 115, Alameda, Calif. 94501. Telephone: (510) 522-1555.

Engage with Verific at:

Email: [email protected]

Website: www.verific.com

LinkedIn: https://www.linkedin.com/company-beta/810695

Facebook: https://www.facebook.com/Verific-Design-Automat[...]

Verific Design Automation and Efinix acknowledge trademarks or registered trademarks of other organizations for their respective products and services.